### Aim:

To understand the basics of KLayout's LVS

Disclaimer:

This document is for personal records only. There is NO WARRANTY on technical correctness.

By Kazzz-S (2023-03-01) original (2023-02-21)

# Part-IV: Re-experiments https://github.com/KLayout/klayout/issues/1304

### 16. Confirmed Issue

| Spic | e netlist reader: should read "M" terminals in DGS o                                                                                          | <b>rder.</b> #13 | 04                      |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------------|

| Oper | klayoutmatthias opened this issue 2 days ago · 0 comments                                                                                     |                  |                         |

|      |                                                                                                                                               |                  |                         |

|      | klayoutmatthias commented <u>2 days ago</u> • edited • Collabo                                                                                | orator 😳 🚥       | Assignees               |

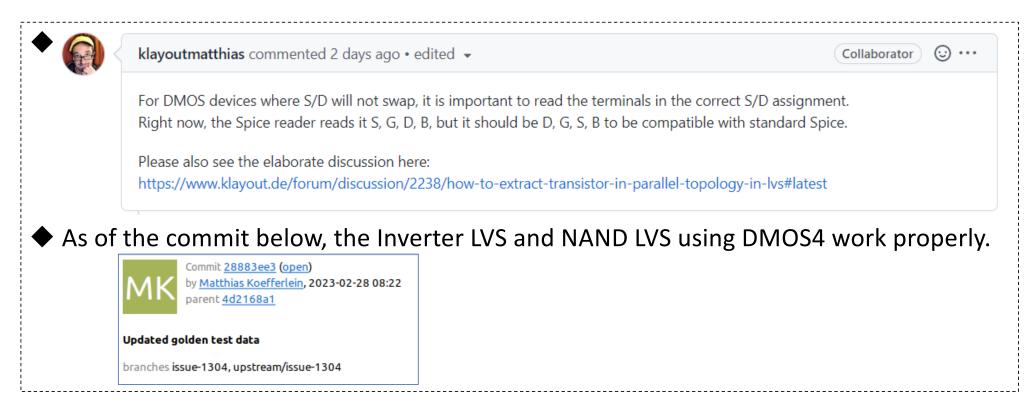

|      | Feb 27, 2023, 7:11 AM GMT+9<br>For DMOS devices where S/D will not swap, it is important to read the terminals in the correct S/D assignment. |                  | 🔞 klayoutmatthias       |

|      | Right now, the Spice reader reads it S, G, D, B, but it should be D, G, S, B to be compatible with standard Spice.                            |                  |                         |

|      | Please also see the elaborate discussion here:                                                                                                |                  | Labels                  |

|      | https://www.klayout.de/forum/discussion/2238/how-to-extract-transistor-in-parallel-topology-in-lvs#latest                                     |                  |                         |

|      |                                                                                                                                               |                  | Projects<br>None vet    |

|      | 8 Realize this 2 days ago                                                                                                                     |                  | None yet                |

|      | Nage and the bug label 2 days ago                                                                                                             |                  | Milestone               |

|      |                                                                                                                                               |                  | 0.28.6                  |

|      | klayoutmatthias added this to the 0.28.6 milestone 2 days ago                                                                                 |                  | Development             |

|      |                                                                                                                                               |                  | No branches or pull rec |

|      | klayoutmatthias pushed a Build the "issue-1304" branch for re-experiments                                                                     |                  |                         |

|      | Fixed issue #1304 (terminal order for MOS devices)                                                                                            | 🗙 0fa9bc6        | Notifications           |

### 16. Confirmed Issue

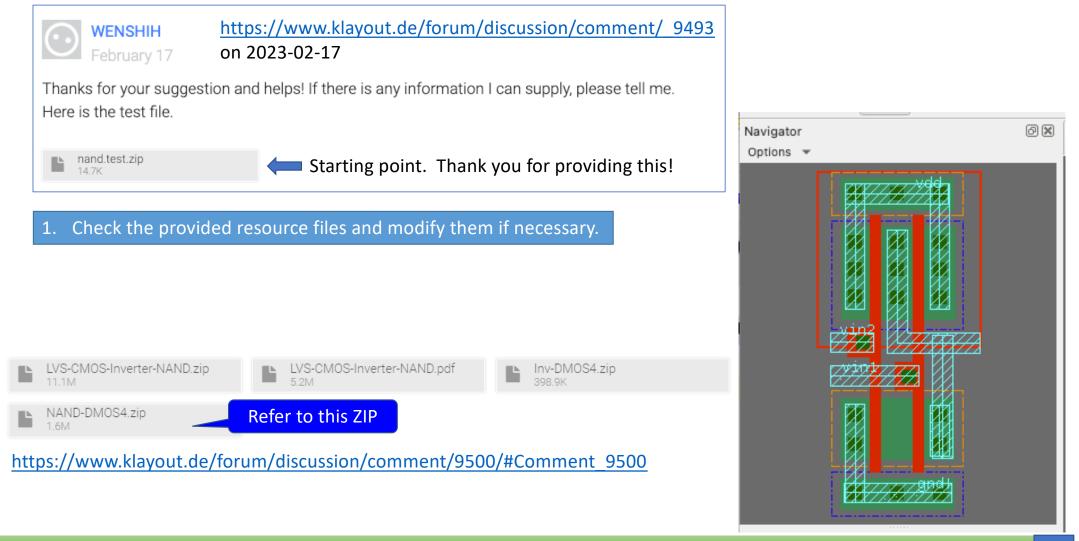

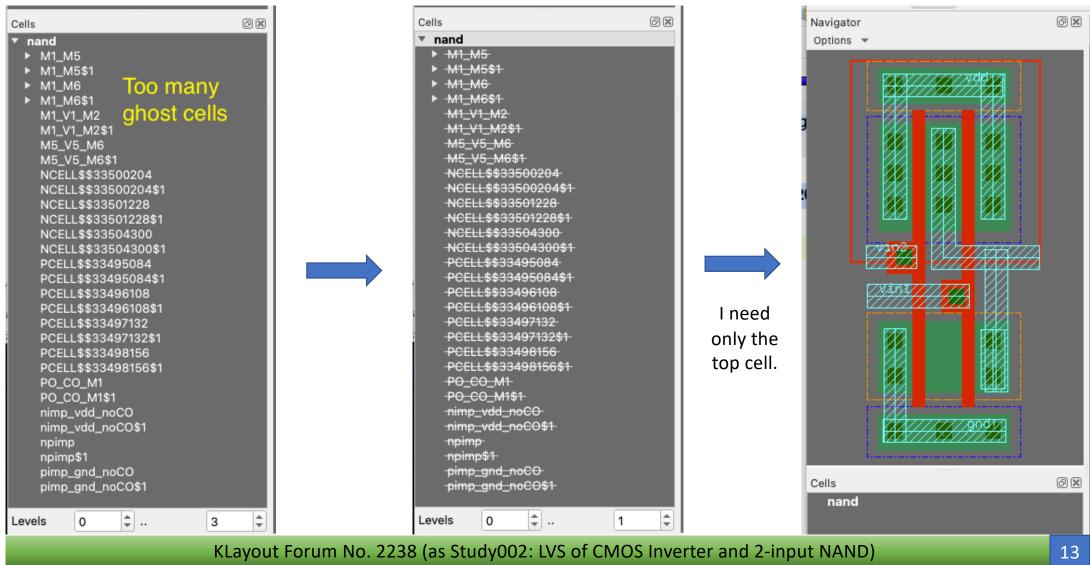

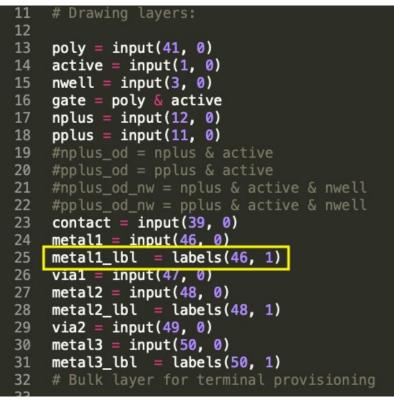

KLayout Forum No. 2238 (as Study002: LVS of CMOS Inverter and 2-input NAND)

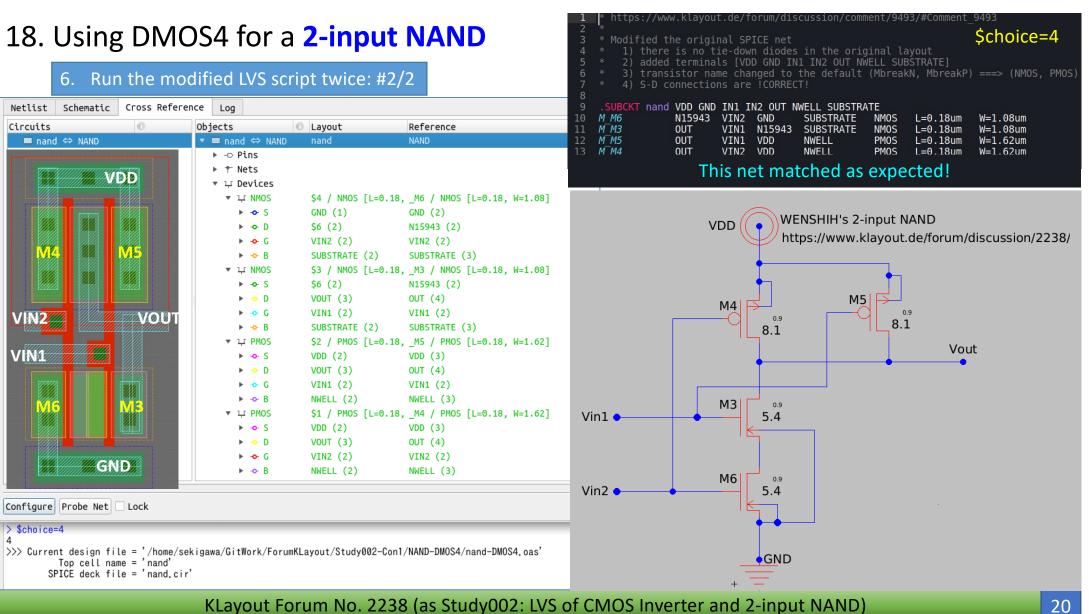

Commit 28883ee3 (open)

KLayout Forum No. 2238 (as Study002: LVS of CMOS Inverter and 2-input NAND)

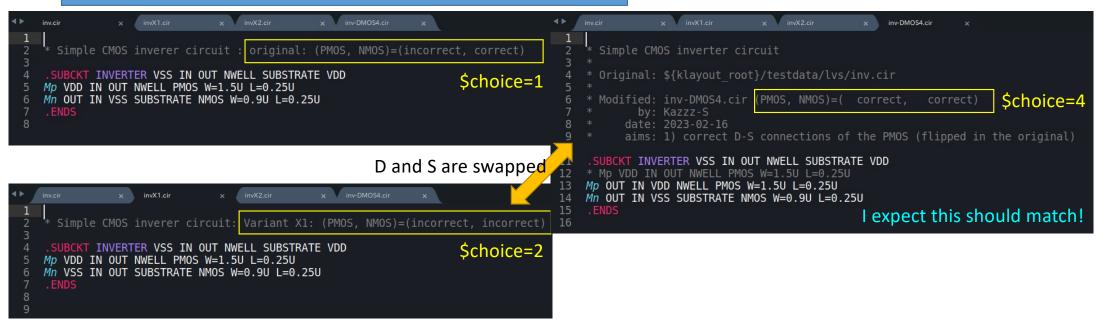

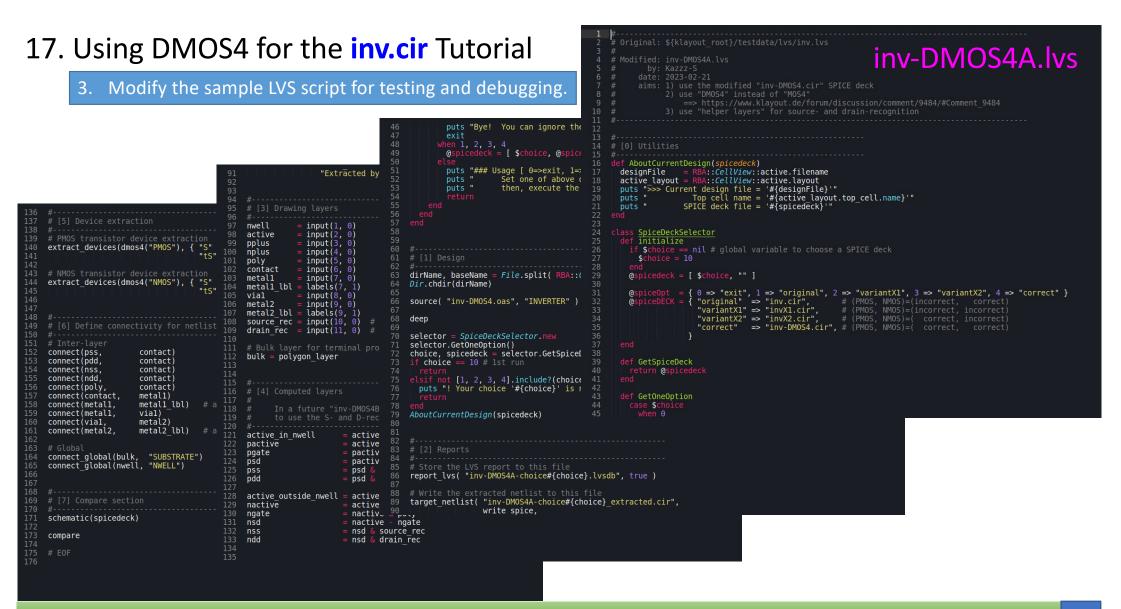

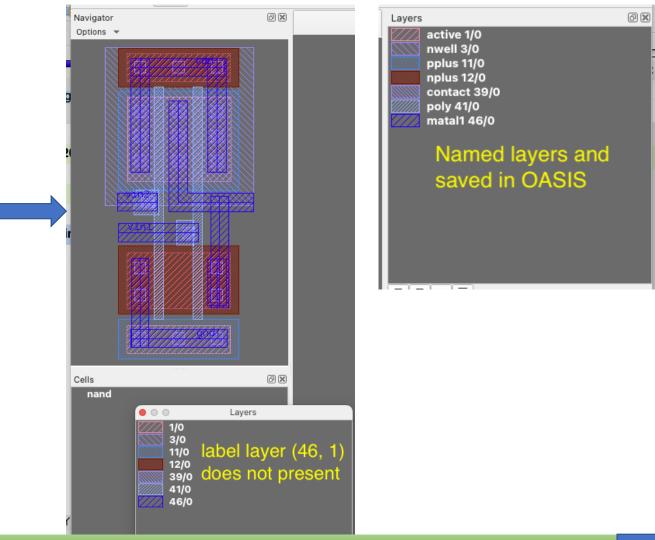

2. Prepare four SPICE deck files to test all S and D combinations.

4. Run the modified LVS script four times: #1/4

| <b>*</b>    | inv.cir  |      | invX1.cir | ×                        | invX2.cir   | × in   | w-DMOS4.cir | ×          |          |

|-------------|----------|------|-----------|--------------------------|-------------|--------|-------------|------------|----------|

| 1           | * Simple | CMOS | inverer   | circuit :                | original:   | (PMOS, | NMOS)=(:    | incorrect, | correct) |

| 3<br>4<br>5 |          |      |           | IN OUT NWE<br>MOS W=1.5U | LL SUBSTRAT | TE VDD |             | \$         | choice=1 |

| 6<br>7      |          |      |           |                          | 0.9U L=0.25 | 50     |             |            |          |

| Netlist Schematic | Cross Referen | ice Log  |                |                     |                          |

|-------------------|---------------|----------|----------------|---------------------|--------------------------|

| Circuits          | 0             | Objects  | 0              | Layout              | Reference                |

| INVERTER          | 0             | 🔻 📖 INVE | RTER 🖨         | INVERTER            | INVERTER                 |

|                   |               | ▶ -⊃ Pi  | .ns            |                     |                          |

|                   |               | ▶ 🕈 Ne   | ets            |                     |                          |

|                   |               | ▼ 부 De   | vices          |                     |                          |

|                   |               | ▼ ↓      | NMOS 🤤         | \$2 / NMOS [L=0.25, | N / NMOS [L=0.25, W=0.9] |

|                   |               | •        | 🔶 S            | VSS (1)             | VSS (2)                  |

|                   |               | •        | - <b>○</b> D   | OUT (2)             | OUT (3)                  |

|                   |               | •        | 🔸 G 🛛 🤤        | IN (2)              | IN (3)                   |

|                   |               | ►        | - <b>о</b> - В | SUBSTRATE (1)       | SUBSTRATE (2)            |

|                   |               | ▼ ↓      | PMOS           | \$1 / PMOS [L=0.25, | P / PMOS [L=0.25, W=1.5] |

|                   |               | ►        | 🔸 S 🛛 🤤        | VDD (1)             | OUT (3)                  |

|                   |               | ►        | 🔸 D 🛛 🤤        | OUT (2)             | VDD (2)                  |

|                   |               | •        | 🔸 G 🛛 🤤        | IN (2)              | IN (3)                   |

|                   |               | •        | - <b>о</b> - В | NWELL (1)           | NWELL (2)                |

|                   |               |          |                |                     |                          |

|                   |               |          |                |                     |                          |

|                   |               |          |                |                     |                          |

Configure Probe Net 🗌 Lock

### > \$choice=1

>>> Current design file = '/home/sekigawa/GitWork/ForumKLayout/Study002-Con1/Inv-DM0S4/inv-DM0S4.oas'

Top cell name = 'INVERTER'

SPICE deck file = 'inv.cir'

4. Run the modified LVS script four times: #2/4

| ••          | inv.cir ×              | invX1.cir   | x in    |           | × inv-I  | OMOS4.cir | ×           |              |

|-------------|------------------------|-------------|---------|-----------|----------|-----------|-------------|--------------|

| 1<br>2<br>2 | * Simple CMOS          | inverer cir | cuit: V | ariant X1 | : (PMOS, | NMOS)=    | (incorrect, | , incorrect) |

| 3<br>4<br>5 | .SUBCKT INVER          |             |         |           | TE VDD   |           | \$          | choice=2     |

| 6<br>7      | Mn VSS IN OUT<br>.ENDS |             |         |           | 50       |           |             |              |

| 8<br>9      | Unlike                 | the previc  | ous ex  | perime    | nt, thi  | s net     | did not ı   | match.       |

| Netlist Schematic | Cross Referen | ce Log                 |                       |                          |

|-------------------|---------------|------------------------|-----------------------|--------------------------|

| Circuits          | 0             | Objects                | Layout                | Reference                |

| INVERTER          | 0             | ▼ 🛄 INVERTER           | S INVERTER            | INVERTER                 |

|                   |               | ▶ -⊃ Pins              |                       |                          |

|                   |               | ▶ 🕆 Nets               |                       |                          |

|                   |               | ▼ 屮 Devices            |                       |                          |

|                   |               | ▼ ⊥ NMOS               | 🤤 \$2 / NMOS [L=0.25, | N / NMOS [L=0.25, W=0.9] |

|                   |               | ▶ <mark>•</mark> S ⇔ D | 🖨 VSS (1)             | VSS (2)                  |

|                   |               | ▶                      | OUT (2)               | OUT (3)                  |

|                   |               | ► <del>•</del> G       | 🖨 IN (2)              | IN (3)                   |

|                   |               | ▶ - <b>०</b> - B       | SUBSTRATE (1)         | SUBSTRATE (2)            |

|                   |               | ▼ ໍ↓ PMOS              | \$1 / PMOS [L=0.25,   | P / PMOS [L=0.25, W=1.5] |

|                   |               | ▶ <del>•</del> S       | 🗢 VDD (1)             | OUT (3)                  |

|                   |               | ▶ - <u></u> D          | 📮 OUT (2)             | VDD (2)                  |

|                   |               | ► <del>•</del> G       | 🖨 IN (2)              | IN (3)                   |

|                   |               | ► 🗢 B                  | NWELL (1)             | NWELL (2)                |

|                   |               |                        |                       |                          |

|                   |               |                        |                       |                          |

Configure Probe Net 🗌 Lock

```

> $choice=2

2

```

>>> Current design file = '/home/sekigawa/GitWork/ForumKLayout/Study002-Con1/Inv-DM0S4/inv-DM0S4.oas'

Top cell name = 'INVERTER'

SPICE deck file = 'invX1.cir'

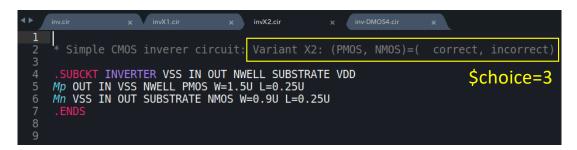

4. Run the modified LVS script four times: #3/4

| <b>4</b> ►  | inv.cir                                                                                         | x invX1.cir | ×        | invX2.cir | × inv-E    | OMOS4.cir | ×        |            |

|-------------|-------------------------------------------------------------------------------------------------|-------------|----------|-----------|------------|-----------|----------|------------|

| 1 2 2       | * Simple CM                                                                                     | 10S inverer | circuit: | Variant   | X2: (PMOS, | NMOS)=(   | correct, | incorrect) |

| 3<br>4<br>5 | .SUBCKT INV                                                                                     |             | \$c      | hoice=3   |            |           |          |            |

| 6<br>7      | Mp OUT IN VSS NWELL PMOS W=1.5U L=0.25U<br>Mn VSS IN OUT SUBSTRATE NMOS W=0.9U L=0.25U<br>.ENDS |             |          |           |            |           |          |            |

| 8           |                                                                                                 |             |          |           |            |           |          |            |

| Netlist Schematic | Cross Referen | ce Log         |       |                     |                          |

|-------------------|---------------|----------------|-------|---------------------|--------------------------|

| Circuits          | 0             | Objects        | 0     | Layout              | Reference                |

| INVERTER          | 0             | 🔻 📖 INVERTER   | ء 🗧   | INVERTER            | INVERTER                 |

|                   |               | ▶ -⊃ Pins      |       |                     |                          |

|                   |               | 🕨 🕈 Nets       |       |                     |                          |

|                   |               | ▼ Ӌ Devic      | es    |                     |                          |

|                   |               | ▼ Ÿ NMO        | os 🤤  | \$2 / NMOS [L=0.25, | N / NMOS [L=0.25, W=0.9] |

|                   |               | ۰ ا            | D⇔S © | OUT (2)             | OUT (3)                  |

|                   |               | ► <del>•</del> | s ⇔ D | VSS (1)             | VSS (3)                  |

|                   |               | ۰ ۱            | G 🤤   | IN (2)              | IN (3)                   |

|                   |               | ► <del>•</del> | В     | SUBSTRATE (1)       | SUBSTRATE (2)            |

|                   |               | ▼ 부 РМС        | os    | \$1 / PMOS [L=0.25, | P / PMOS [L=0.25, W=1.5] |

|                   |               | ► <del>•</del> | s 🤤   | VDD (1)             | VSS (3)                  |

|                   |               | ۰ ا            | D 🤤   | OUT (2)             | OUT (3)                  |

|                   |               | ۰ ا            | G 🤤   | IN (2)              | IN (3)                   |

|                   |               | ► <del>•</del> | В     | NWELL (1)           | NWELL (2)                |

|                   |               |                |       |                     |                          |

|                   |               | L              |       |                     |                          |

Configure Probe Net 🗌 Lock

#### > \$choice=3 3

>>> Current design file = '/home/sekigawa/GitWork/ForumKLayout/Study002-Con1/Inv-DM0S4/inv-DM0S4.oas'

Top cell name = 'INVERTER'

SPICE deck file = 'invX2.cir'

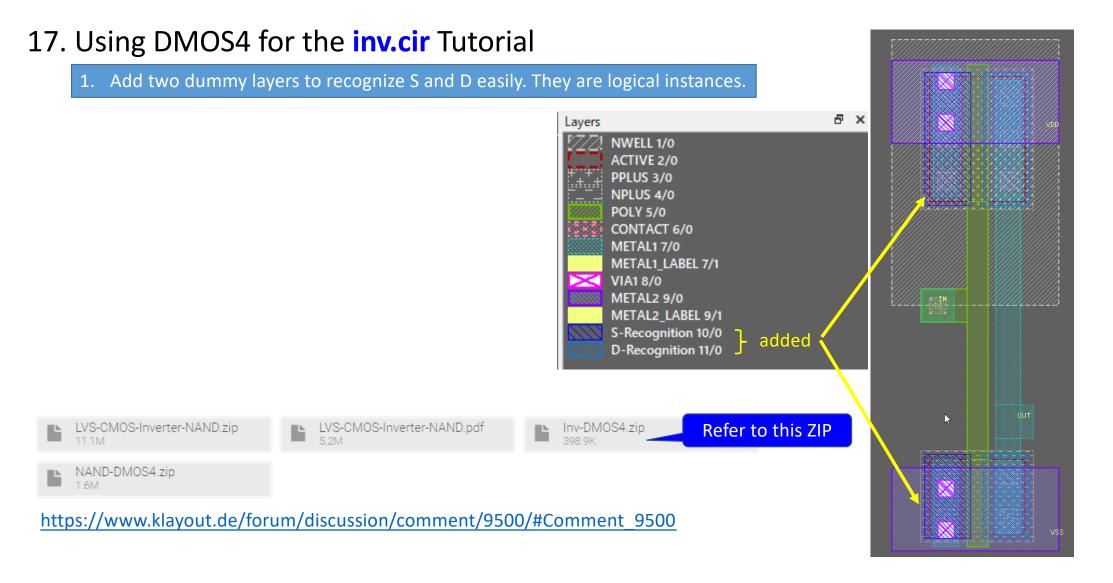

| 17. Using DMOS4 for t<br>4. Run the modified LVS scri                                                                                                           |                                                                         | <pre> inv.cir x invX1.cir x invX2.cir x inv-DMOS4.cir x  * Simple CMOS inverter circuit * 4 * Original: \${klayout_root}/testdata/lvs/inv.cir * 6 * Modified: inv-DMOS4.cir (PMOS, NMOS)=( correct, correct) \$choice=4 7 * by: Kazzz-S 8 * date: 2023-02-16 9 * aims: 1) correct D-S connections of the PMOS (flipped in the original) </pre> |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Netlist         Schematic         Cross Reference         Log           Circuits         0         0bjects                                                      |                                                                         | 10<br>11 .SUBCKT INVERTER VSS IN OUT NWELL SUBSTRATE VDD<br>12 * Mp VDD IN OUT NWELL PMOS W=1.5U L=0.25U                                                                                                                                                                                                                                       |

| INVERTER  INVERTER  INVERTER  IN  F→□  F  T  V  V  V  V  V  V  V  V  V  V  V  V                                                                                 | INVERTER         INVERTER           Pins         Nets           Devices | <pre>13 Mp OUT IN VDD NWELL PMOS W=1.5U L=0.25U<br/>14 Mn OUT IN VSS SUBSTRATE NMOS W=0.9U L=0.25U<br/>15 .ENDS This net matched as expected!<br/>5, N / NMOS [L=0.25, W=0.9]<br/>VSS (2)<br/>OUT (3)<br/>IN (3)<br/>SUBSTRATE (2)<br/>5, P / PMOS [L=0.25, W=1.5]<br/>VDD (2)<br/>OUT (3)<br/>IN (3)<br/>NWELL (2)</pre>                      |

| Configure Probe Net Lock<br>> \$choice=4<br>4<br>>>> Current design file = '/home/sekigawa/G<br>Top cell name = 'INVERTER'<br>SPICE deck file = 'inv-DMOS4.cir' | itWork/ForumKLayout/Study002-Con1/Inv-I                                 | DMOS4/inv-DMOS4.oas'                                                                                                                                                                                                                                                                                                                           |

| KLayout Fo                                                                                                                                                      | rum No. 2238 (as Study002: L\                                           | VS of CMOS Inverter and 2-input NAND) 11                                                                                                                                                                                                                                                                                                       |

### 19. Summary and Conclusions

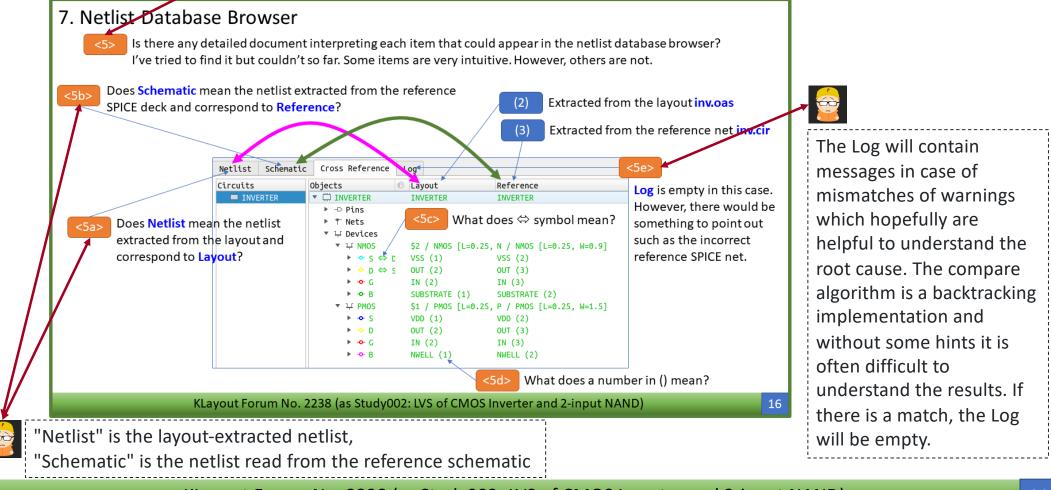

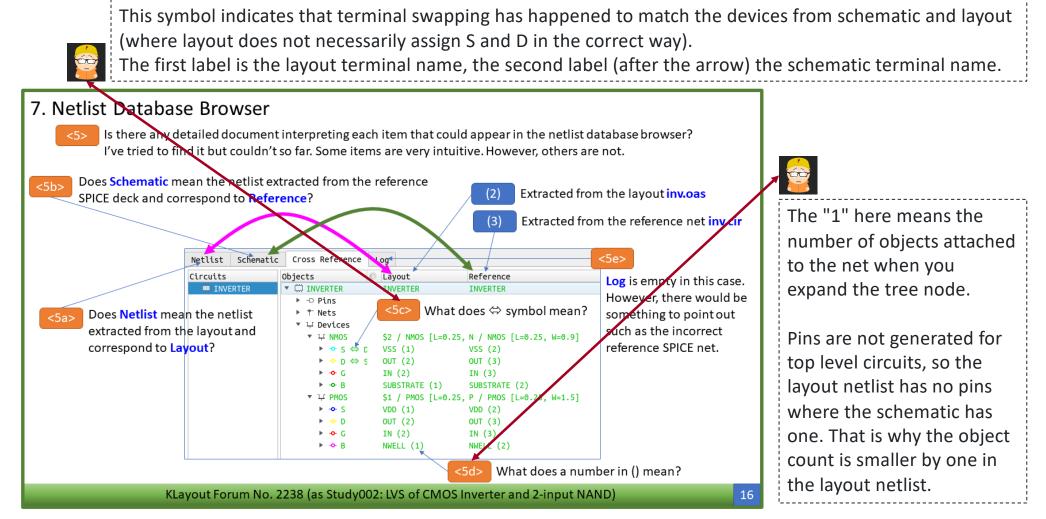

## **Part-V: Appendix** *Q&A on Netlist Database Browser*

https://www.klayout.de/forum/discussion/comment/9504/#Comment\_9504

Detailed documentation: honestly there is no full documentation about the result browser. Maybe the information here is helpful: <u>https://www.klayout.de/doc-</u> <u>qt5/manual/lvs\_compare.html#h2-348</u>, specifically "how the compare algorithm works".