Howdy, Stranger!

It looks like you're new here. If you want to get involved, click one of these buttons!

Quick Links

Combining fingered MOS devices / LVS of combined MOS devices

Hello everyone,

Question first: How can I perform an LVS check of MOS transistors while treating fingered devices as equal to combined devices?

A while ago I started using KLayout LVS for verifying the output of the LibreCell standard-cell generator. Now I'm stuck with the following easy problem: The extracted netlist seems to have devices combined, while the reference netlist has not. This makes the LVS check fail. I tried to simplify() the reference netlist. But this has no effect while on the extracted netlist this works. (Maybe because S/D don't match in the reference netlist?)

A working solution is to not combine the devices in the extracted netlist. However, I would like to find a more generic approach because the layout generator may or may not decide to split or combine transistors.

This is how the netlists look:

LVS extracted netlist:

circuit INVX4 (A=A,GND=GND,Y=Y,VDD=VDD);

device PMOS $1 (S=Y,G=A,D=VDD) (L=0.05,W=2,AS=0.45,AD=0.3525,PS=4.9,PD=2.75);

device NMOS $3 (S=Y,G=A,D=GND) (L=0.05,W=1,AS=0.20125,AD=0.20125,PS=2.325,PD=2.325);

end;

LVS reference netlist:

circuit INVX4 (VDD=VDD,GND=GND,Y=Y,A=A);

device PMOS '0' (S=Y,G=A,D=VDD) (L=0.05,W=1,AS=0,AD=0,PS=0,PD=0);

device PMOS '1' (S=VDD,G=A,D=Y) (L=0.05,W=1,AS=0,AD=0,PS=0,PD=0);

device NMOS '2' (S=Y,G=A,D=GND) (L=0.05,W=0.5,AS=0,AD=0,PS=0,PD=0);

device NMOS '3' (S=GND,G=A,D=Y) (L=0.05,W=0.5,AS=0,AD=0,PS=0,PD=0);

end;

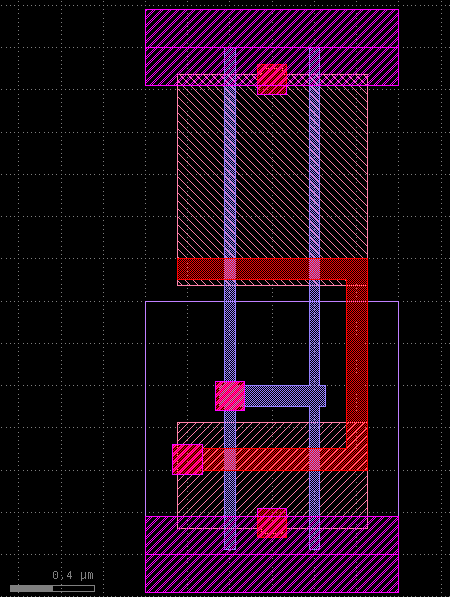

Here is the layout:

Thanks in advance!

Comments

Hi Thomas,

my suggestion would be to combine the devices on the reference netlist before compare. So the "normalized" way is to see the devices as combined ones. At least for compare.

I don't know if there is a reason to keep devices separate in the schematic. Maybe for convenience or maybe for simulation. Or it's just a matter of how the netlists are written.

In the extracted netlist, device combination is part of the "simplify" scheme. In the reference netlist, I'd not use "simplify" because it has side effects such as introducing pins you might not want to see. But you can use "combine_devices" on the reference netlist to achieve the normalization to singe devices:

(Caution: badly documented feature - "schematic" without arguments returns the schematic Netlist object)

Best regards,

Matthias

Thanks Matthias for answering!

Unfortunately, in my case combine_devices()` seems to have no effect on the reference netlist. But on the extracted netlist it does.

I'm using the Python API.

The following code shows how I extract the netlist (all the connectivity setup is omitted) and how I compare the netlists. This is the version that works as long as both netlists have exactly the same transistors. It is sensitive to transistor folding/combining though.

The

reference.combine_devices()somehow does not combine anything. Could it be thatcombine_devices()is not aware that it is allowed to swap source and drain? I'm also using a customdb.NetlistSpiceReaderDelegateimplementation for reading 4-terminal MOS transistors as 3-terminal transistors. Maybe I'm doing something wrong there.This is what I use to read the netlist.

The full file can be found here: https://codeberg.org/tok/librecell/src/commit/0632cf17429c37b152f1b1f356e13c5a762a921a/librecell-layout/lclayout/lvs/lvs.py

Thanks a lot for your help!

Hi Thomas,

Hmm ... I don't see an obvious reason it shouldn't work ...

To start with debugging, I can give a positive example. I do the following using your Spice reader delegate class and the function:

With this netlist in "test.cir":

I get the following results:

So basically the function should work.

One requirement is that the transistor lengths are identical. So this will not combine the devices:

Maybe this is the case here?

Matthias

Thanks for the example! I will try this.

The transistor length are all equal.

Hi Matthias,

I found out what causes my problem but I don't know yet what happens exactly.

In the example above I forgot about a detail: The netlist I load contains possibly many circuits but I'm interested only in one. The extracted layout also contains only one circuit of a standard-cell. Therefore I isolate a single circuit and put it into a new netlist. This is what seems to make

combine_devices()fail.The simplest solution I found is to run

combine_devices()on the full netlist before isolating the circuit.Is there a better way how to do this? Ideally I would not have to care about how the reference netlist object was created.

Here is an example to reproduce the behaviour.

Thanks so much!

Hi Thomas,

sorry for this long delay - I was entirely absorbed by this nasty MacOS issue: https://github.com/KLayout/klayout/issues/589 ...

Regarding your question: adding a foreign Circuit into a new Netlist is not supported I'm afraid. A circuit will carry more references, namely into subcircuits and device classes. When you add a device into a different netlist, these references are not translated and will point to the old netlist. This makes combine_devices fail.

But there is a very simple solution to combine_devices on a single circuit: simply use Circuit#combine_devices

If you have to extract a circuit from a netlist, the only way currently is to deleted every other circuit you don't need

Best regards,

Matthias

Hello Matthias!

No problem !

Thanks for the hint! Just changed my code and now do it that way by deleting all non-used circuits. Works fine!

Bests,

Thomas