Howdy, Stranger!

It looks like you're new here. If you want to get involved, click one of these buttons!

Quick Links

split_gate for netlist object

Hi @Matthias

I saw "split_gate" feature(let us reduce gate) in klayout new version. It is very usefull ![]() .

.

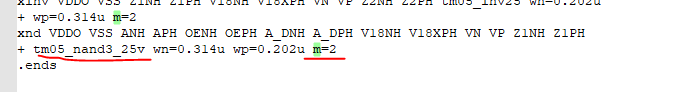

I think it will be more usefull if we have this feature in netlist object also. Because schematic designer use multiple factor like below some time:

So if we use split_gate for netlist so we need run this feature for netlist of schematic also.

Thank you!

dai

Comments

Well crafted SPICE models will give you different (subtly)

outcomes from (say) a 100/0.18 and a (10)10/0.18 FET.

Your verification ahould not ignore or obscure this if any

analog matching interests are involved. Probably want to

make this a "switch" in the LVS (where you can decide

whether or not to allow) rather than in the extract, where

it may get "baked in" but invisibly so.

Hi Jim,

"split_gates" is not available for schematic, but you can easily add this feature:

Regarding extraction (and compare I assume) of the finger ("m") parameter: I think that can be added, but I see a number of open questions - e.g. how to add two devices with different widths.

Kind regards,

Matthias

Hi @Matthes ,

It works perfectly

Thank you,

dai