Howdy, Stranger!

It looks like you're new here. If you want to get involved, click one of these buttons!

Quick Links

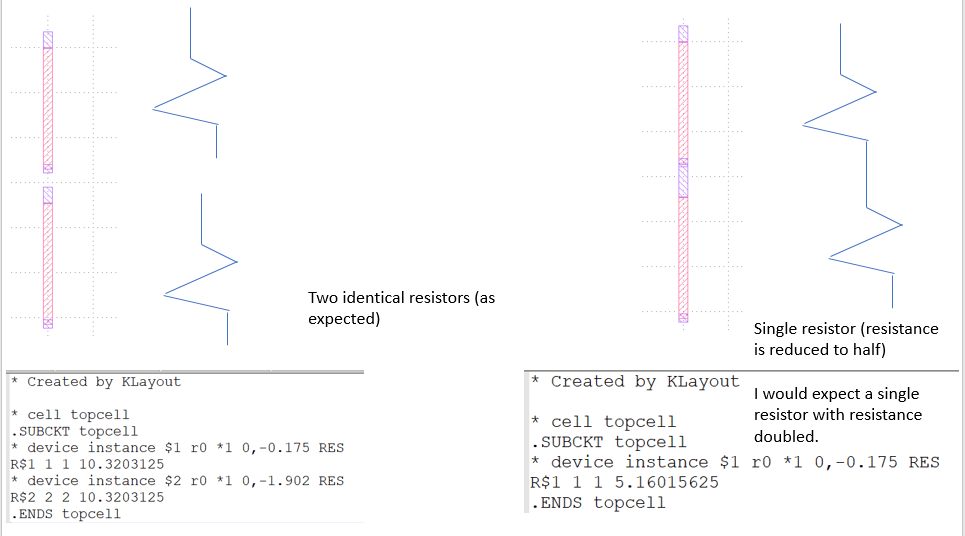

Layout view of resistors

Hello, I am trying to learn the concepts in LVS and device extraction. I am using an LVS script to automatically generate netlists.

I have a basic question. I don't understand why the resistance reduces to half even though I connect the resistors in series (or at least I think I connect them in series ![]() . But it looks like they are connected parallel)

. But it looks like they are connected parallel)

The following layouts consist of two resistors. One of them has separate and the other has connected resistors. When I produce the netlist you see the resistance values as 10.32 and 5.16. I don't understand why resistance reduces to half when I connect these two resistors. Shouldn't they become a single resistor with resistance doubled (since they are connected in series. -or am I wrong? Are they actually parallel?)

If you can make an explanation it would be really helpful! (By the way is there a reference (book etc. ) where I can check how basic electronic components in layout view look like? (Instead of the logical view)

Thanks!

PS: This is the LVS code I use to automatically generate netlists

target_netlist("resistor2.cir", write_spice, "Created by KLayout")

deep

# Produce LVS report

report_lvs

res_layer = input(1,0)

contact_layer = input(2,0)

bulk = polygon_layer

sheet_rho = 1

model_name = "RES"

extract_devices(resistor(model_name, sheet_rho), { "R" => res_layer, "C" => contact_layer })

connect(res_layer,contact_layer)

#connect_global(bulk, "SUBSTRATE")

report_netlist("resistor.l2n")

# Netlist normalization

netlist.simplify

Comments

Whether they are series or parallel depends on

whether the endcaps are the same net or different.

The netlisting appears to think they are the same

net. But "why?" is probably the question.

Now there's something funny about the two

endcaps of both resistor segments, as if perhaps

the "longer" one is also contacting "something"

(NWell? Substrate? Or just a non-identical detail

layout?) as is the norm on implanted resistors

of single stripe - one contact also grabs the

isolation region. Then if the isolation is treated

as a "local global net" (i.e. extraction logic calls

it an ohmic short) than permute-parallel rules

(forget what klayout calls this) might give you

the outcome you're seeing.

Following and testing results are here code follow's

The test gds can be found here

https://github.com/hgroller/test_res

Ege_Bey,

You can find more info located here, Matthias has provided a dummy pdk.

https://github.com/klayoutmatthias/si4all.git

Tracy

Hello! Sorry for my late reply! Thank you very much for your help and providing this nice resistor layout and the code !

!

Ege_Bey,

Any time this was buried in the forum and many thanks to Matthias for providing the dummy pdk

@tagger5896

Thanks for the sample. To be frank it seems to be working, although it produces each resistor in a separate cell because that's how it was designed.

If you want to get rid of the RES2 device cell, use this:

I have also added this

At the beginning which gives me this nice netlist view:

In this case, resistors don't get combined as the middle node is a pin.

When I remove the "OUT" labels, this pin is gone and I get a nice combination of the resistory in series:

So my conclusion is that it's working.

In your previous case, I think the problem was that you shortened the resistors by connecting the resistor layer (which is essentially the body) and the contacts. This makes the body a conductive layer which shorts everything:

This is also the reason why "R$1" in your right netlist is connected to net "1" with both terminals.

Classic joke (KiCad version):

Matthias

@Matthias,

Thanks for the valuable input,

I am still learning Klayout in's and outs .

Tracy